TNANO Article in focus: May 2016

From the May 2016 issue of IEEE Transactions on Nanotechnology

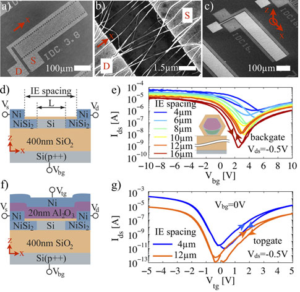

Printable Parallel Arrays of Si Nanowire Schottky-Barrier-FETs With Tunable Polarity for Complementary Logic

by Sebastian Pregl; André Heinzig; Larysa Baraban; Gianaurelio Cuniberti; Thomas Mikolajick; Walter M. Weber T-NANO, Vol. 15, Issue 3, pp. 549 – 556, May 2016.

Abstract: In this paper, we present a novel technology of printable bottom-up grown Si nanowire parallel arrays for low-dissipation power electronics. Parallel aligned layers of monocrystalline Si nanowires can be deposited on arbitrary substrates over large areas by the printing process. The presented transistors consist of parallel arrays of longitudinal NiSi2-Si-NiSi2 nanowire heterostructures, which naturally show ambipolar transistor behavior when a single gate is employed. By a double gate architecture, a reconfigurable transitor component is created, for which unipolar p- or n-type characteristics can be obtained depending on the polarity of the second gate. Transfer and output characteristics of these transistors on a Si/SiO2 substrate with back gate, top gate, and reconfigurable double gate architecture are presented here in detail. Very high on/off-current ratios of over 108 are achieved with very low off-currents. Due to the high number of nanowires incorporated into individual parallel arrays, output currents of 0.5 mA and a high yield of functional transistors of close to 100% at nanowire coated areas are demonstrated.