TNANO Article in focus: September 2016

From the September 2016 issue of IEEE Transactions on Nanotechnology

Methodology and Design of a Massively Parallel Memristive Stateful IMPLY Logic-Based Reconfigurable Architecture

by YYasunao Katayama; Toshiyuki Yamane; Daiju Nakano; Ryosho Nakane; Gouhei Tanaka

T-NANO, Vol. 15, Issue 5, pp. 762 – 769, September 2016.

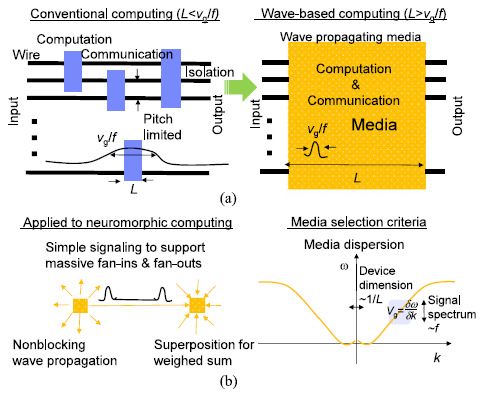

Abstract: We present a framework of wave-based neuromorphic computing aiming at brain-like capabilities and efficiencies with nanoscale device integration. We take advantage of the unique nature of elastic nondissipative wave dynamics in both computations and IO communications in between as a means to natively implement and execute neuromorphic computing functions such as weighted sum in a spatiotemporal manner. Lower bound analysis based on a memory model and wave group velocity scaling is provided for conceptual evaluations.